振鈴現(xiàn)象屬于信號完整性問題,其解決方法通常為端接匹配技術(shù)。

進行信號完整性的分析需用到IBIS 模型和EDA工具,其中IBIS(Input/Output Buffer Information Specification)模型是一種基于V/I曲線的對1/O BUFFER快速準確建模的方法,是反映芯片驅(qū)動和接收電氣特性的一種國際標準;

它提供一種標準的文件格式來記錄如驅(qū)動源輸出阻抗、上升/下 降時間及輸入負載等參數(shù),適合做振鈴和串?dāng)_等高頻效應(yīng)的計算與仿真。

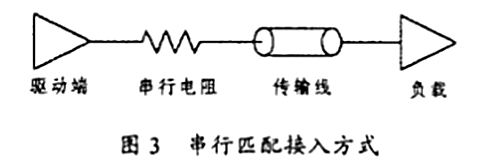

1、串行匹配法

串行匹配,即使驅(qū)動端的阻抗與傳輸線的阻抗相匹配,其接入方式如圖3.

串行匹配即是在傳輸線模型前加入一個串行電阻,通過調(diào)整電阻值來使驅(qū)動端阻抗和傳輸線阻抗一致,通常串入電阻的阻抗加上驅(qū)動端阻抗應(yīng)比傳輸線上的阻抗略大一些。

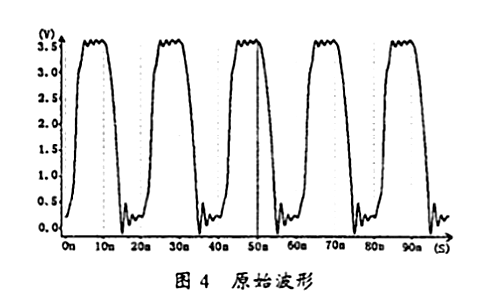

在未串接電阻時,信號的原始波形如圖4所示。

可以看到在負載端有振幅近500mV的振鈴現(xiàn)象。

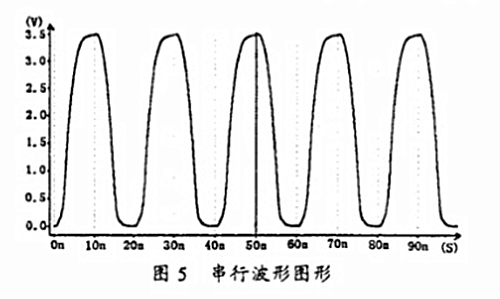

當(dāng)接入500電阻時,信號的波形如圖5所示。

由圖5可知,振鈴現(xiàn)象所產(chǎn)生的毛刺已被消除。串行匹配只需在電路中串入一個電阻,不直接與電源相接,因此功耗較小,連接簡單;

但其也有不足之處:串入的電阻會在源端和自身之間產(chǎn)生反射信號,如果有其他輸入信號的話,會對其邏輯狀態(tài)造成影響;并因為增加了電路的RC常數(shù)會導(dǎo)致信號的上升時間變緩,所以在超高速電路中不太適用。

〈烜芯微/XXW〉專業(yè)制造二極管,三極管,MOS管,橋堆等,20年,工廠直銷省20%,上萬家電路電器生產(chǎn)企業(yè)選用,專業(yè)的工程師幫您穩(wěn)定好每一批產(chǎn)品,如果您有遇到什么需要幫助解決的,可以直接聯(lián)系下方的聯(lián)系號碼或加QQ/微信,由我們的銷售經(jīng)理給您精準的報價以及產(chǎn)品介紹

聯(lián)系號碼:18923864027(同微信)

QQ:709211280